Cross-Platform NPU Analysis

Architectural Insights and Optimization Guidelines for On-Device LLM Inference

随着大型语言模型(LLM)在端侧设备上的应用日益增多,神经处理单元(NPU)作为关键的硬件加速器,其架构特性和性能表现对模型推理效率起着决定性作用。然而,当前移动NPU市场呈现高度碎片化的特征,主流厂商如Qualcomm、MediaTek和Apple采用了截然不同的架构设计和软件生态策略,为跨平台LLM推理框架(如mllm)的优化带来了巨大挑战。

本报告旨在系统性地分析和比较Qualcomm Hexagon NPU、MediaTek APU及Apple Neural Engine (ANE)的核心技术特征,揭示其架构差异、性能瓶颈与优化潜力。通过深入剖析,我们提炼出通用的NPU优化原则,为mllm框架的跨平台支持提供数据驱动的决策依据和具体的技术优化指导,最终目标是实现模型与硬件的深度协同设计(co-design),充分释放端侧AI的潜力。

Architecture & Design Philosophy

三大平台的NPU在计算单元、内存层次和数据流设计上展现了迥异的设计哲学

计算单元设计

Hexagon NPU采用融合加速器架构,包含标量加速器(Scalar Accelerator)、矢量加速器(Vector Accelerator)和张量加速器(Tensor Accelerator)三种计算单元。这种融合设计使得不同类型的计算任务可以在最适合的加速器上执行,实现性能和功耗的最佳平衡。

内存系统设计

大型专用共享内存(Large Dedicated Shared Memory)是Hexagon NPU的关键特性。这个共享内存允许三个加速器之间高效地共享和移动数据,减少了数据传输开销。根据llm.npu论文的发现,内存带宽是NPU的主要瓶颈之一,因此这种内存设计对性能至关重要。

核心洞察

Qualcomm的架构最为透明和灵活,其融合设计和大型共享内存为细粒度优化提供了可能,但也对开发者提出了更高的要求。在LLM推理中,Hexagon NPU在prefill阶段表现优异,通过最大化整数计算利用率实现显著的性能提升。

Performance & Power Characteristics

NPU的性能不仅取决于理论峰值算力,更在于其在实际LLM推理场景中的表现

LLM推理特征

Prefill优势显著:llm.npu论文明确指出其在Prefill阶段利用整数计算有巨大优势。TTFT仅需0.12秒,8-bit精度下性能翻倍。

精度支持

原生支持INT8、INT4、FP16,为性能与精度的权衡提供最大灵活性。

功耗特性

强调"无与伦比的功耗效率",是其核心卖点之一。

LLM推理特征

APU 790专为生成式AI设计,与LiteRT配合有12倍加速。支持从小型到大型的多种模型规模。

精度支持

支持灵活的量化方案,但具体支持的精度类型细节较少。

功耗特性

明确提及"第二代热优化封装设计"和"多核功耗节省33%",在热管理方面有系统性考虑。

LLM推理特征

Transformer优化参考实现表明其对整个推理流程都有优化。经过优化的模型速度提升最高10倍,内存消耗减少14倍。

精度支持

主要针对FP16进行优化,这是其硬件的核心数据类型。

功耗特性

强调"高能效",是其设计初衷之一。M4达到38 TOPS峰值性能,是营销重点。

Qualcomm和MediaTek更侧重于展示在实际应用(如LLM推理)中的性能提升,而Apple则倾向于宣传理论峰值性能。这表明NPU的实际效率受到架构、软件栈和模型优化的严重影响。

llm.npu的发现揭示了NPU在LLM推理中的一个关键优势区间:Prefill阶段。这为跨平台优化提供了重要思路。无论是Qualcomm的带宽瓶颈,还是Apple的内存布局限制,都表明内存系统是决定NPU处理LLM能力的关键。

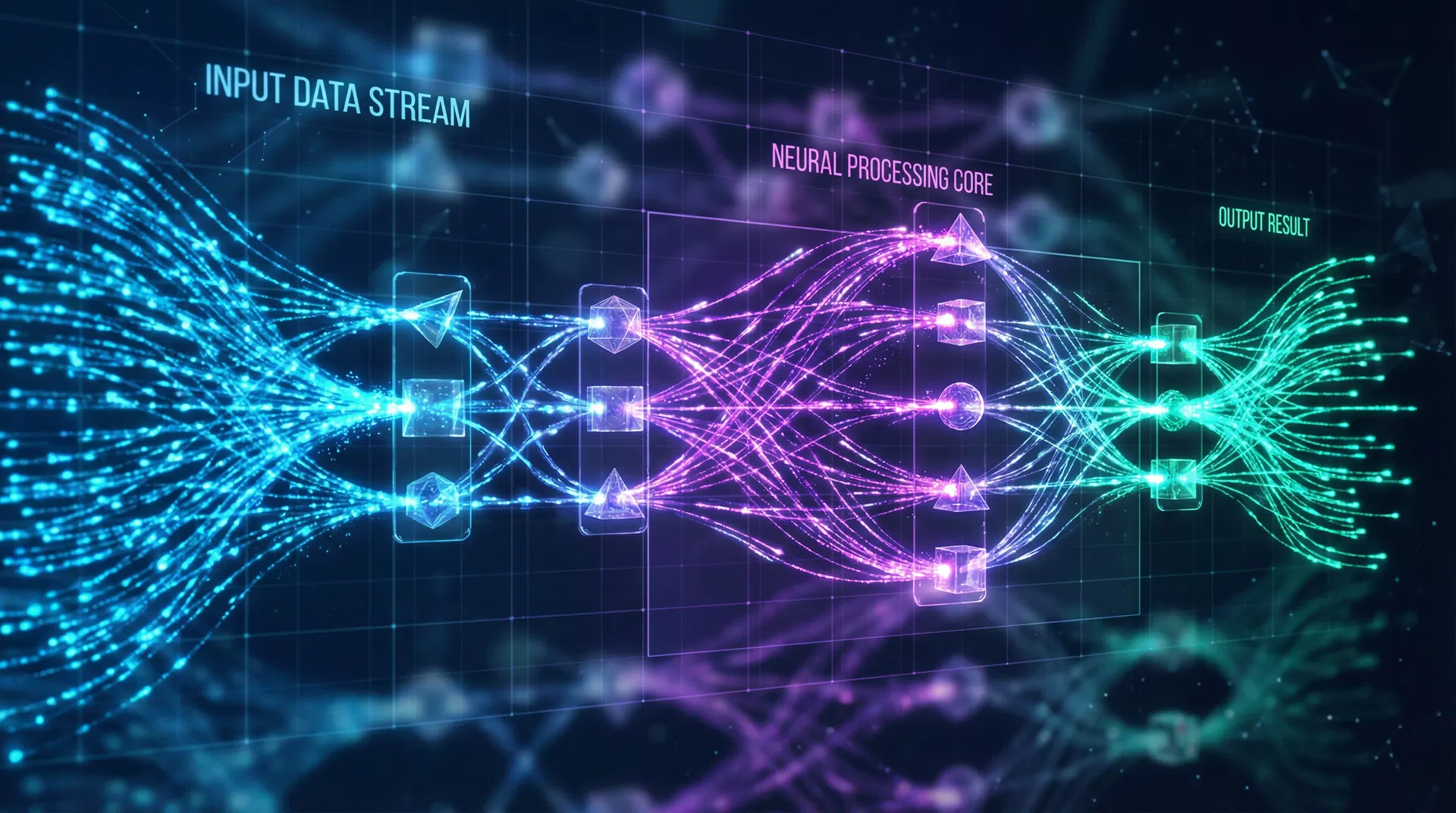

NPU Data Flow Visualization

数据从输入流(电蓝)经过神经处理核心(霓虹紫)转换为输出结果(青绿),展示了NPU的高速计算流程

Optimization Guidelines for mllm

基于跨平台分析,为mllm框架提出的通用NPU优化原则

内存是所有平台的共同瓶颈。mllm的优化策略应围绕"减少数据搬运"和"提高内存访问效率"展开。具体技术包括:

- 算子融合(Operator Fusion):减少中间结果的读写

- 分块处理(Tiling):将大张量分割成小块以提高缓存命中率

- KV Cache优化:研究KV Cache的压缩、量化和淘汰策略

本报告系统地分析了Qualcomm、MediaTek和Apple三家主流移动NPU的架构、性能、功耗和软件生态。分析表明,尽管各平台设计理念迥异,但都面临着内存瓶颈、异构调度和软件优化等共同挑战。

Qualcomm的开放性和灵活性使其成为mllm这类追求极致性能框架的理想合作伙伴,而Apple的封闭生态则构成了主要的适配壁垒。我们提出的五项通用优化原则——拥抱异构、数据布局优先、关注内存、统一量化和后端编译,为mllm从单一平台优化走向跨平台支持提供了清晰的技术路线图。

完成这项"保底"的理论分析工作,不仅为mllm的未来发展奠定了坚实基础,也为整个端侧LLM领域提供了宝贵的架构洞察和工程实践指导。